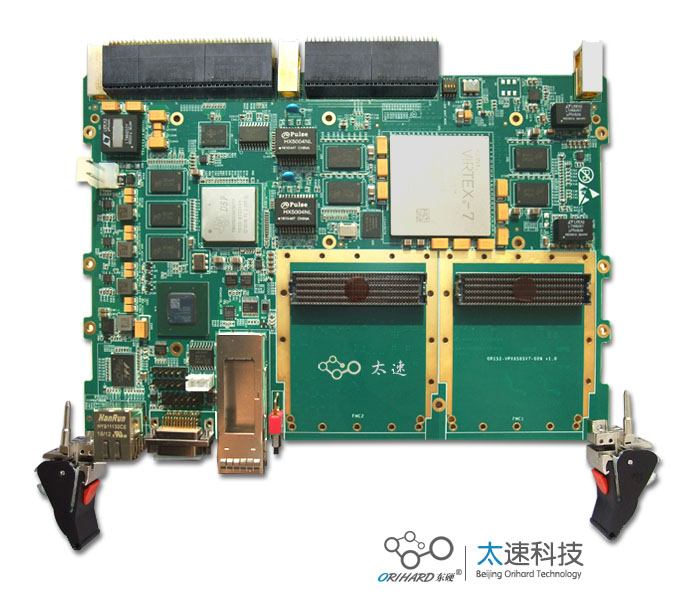

本板卡基于标准6U VPX 架构,为通用高性能信号处理平台,系我公司自主研发。板卡采用一片TI DSP TMS320C6678和一片Xilinx公司Virtex 7系列的FPGA XC7V690T-2FFG1761I作为主处理器,Xilinx 的Aritex XC7A200T作为辅助处理器。XC7A200T负责管理板卡的上电时序,时钟配置,系统及模块复位,程序重配等。为您提供了丰富的运算资源。如图 1所示:

● VITA46.0 VPX Base Standard

● VITA46.3 Serial RapidIO on VPX Fabric Connector

● VITA46.4 PCI Express on VPX Fabric Connector

● VITA46.7 Ethernet on VPX Fabric Connector

● DSP外挂一簇DDR3,数据位宽64bit,容量2GB;数据速率1333MHz;

● DSP外挂NorFlash容量32MB;

● DSP采用EMIF16-NorFlash加载模式;

● DSP连接一路1000BASE-T千兆以太网至前面板;

● DSP连接一路1000BASE-T千兆以太网至VPX P4;

● DSP连接PCIe x2 至VPX P2;

● FPGA外挂两簇DDR3,每簇容量4GB,位宽64bit,总容量8GB;数据速率1600MHz;

● FPGA 外挂NorFlash容量128MB;

● FPGA的加载模式为BPI模式;

● FPGA外接2路FMC-HPC;

● FPGA 连接GTH x8至VPX P1;

● FPGA 连接GTH x4至VPX P2;

● FPGA 连接一路QSFP+至前面板;光口速率40Gbps;

● DSP和FPGA通过 SRIO x4 @ 5.0Gbps /per Lnae互联;

● DSP和FPGA实现GPIO,SPI 互联;

● DSP和CFPGA 实现GPIO,SPI,EMIF互联;

● FPGA和CFPGA实现GPIO 互联;

● CFPGA 连接一路1000BASE-T千兆以太网至VPX P4。

● 板卡要求工业级芯片。结构满足抗震要求。

● 工作温度:商业级 0℃ ~ +55℃,工业级-40℃~+85℃

● 工作湿度:10%~80%

● 单电源供电,整板功耗:40W

● 电压:DC +12V,5A

● 纹波:≤10%

信号处理,无线电通信领域。

七、采集存储计算一体应用

本应用模式,是通过VPX 进行扩展后板,接入四路M.2的固态硬盘存储。

每块存储盘与FPGA之间采用PCIE3.0 x4接口,可将单块存储盘的性能都得到充分发挥。例如:单盘持续读写带宽≥2GB/s,则单盘的存储阵列持续读写带宽≥2GB/s;当多块盘并行工作时,存储阵列读写带宽成指数增长,2块盘则≥4GB/s,4块盘则≥8GB/s,以此类推。

存储阵列的存储容量由单盘配置决定,目前单块NVME存储盘存储容量可选择512GB、1TB、2TB、4TB、8TB、16TB。例如配置4块存储盘,则存储阵列容量最高可达64TB。

硬盘管理通过文件系统,FPGA的PCIeX4与 6U VPX主板互联,操作系统直接映射管理硬盘,也可以通过前面板QSFP+ 光纤导出给其他服务器设备。

FMC子卡可以扩展高速AD,DA, 也可以扩展8路光纤,图像子卡等。

本方案优势就是集中的进行采集,存储,计算一体化,降低硬件成本、功耗,减小设备体积、重量。带来的问题就是FPGA程序集成度很大,开发难度高。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。